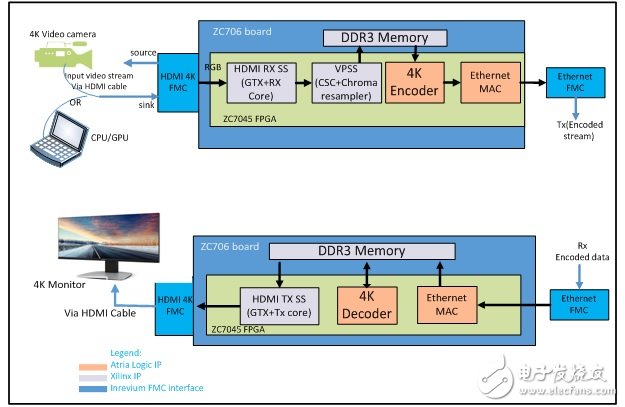

Atria Logic has successfully ported its H.264 codec IP, including the AL-H264E-4KI422-HW encoder and AL-H264D-4KI422-HW decoder, to the Xilinx Zynq Z-7045 SoC. This integration enables high-performance UHD 4K @ 60fps video streaming, as illustrated in the following diagram:

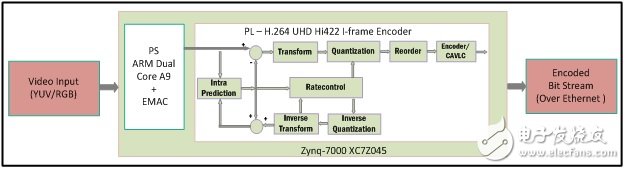

The block diagram below illustrates the H.264 codec IP design developed by Atria Logic.

The AL-H264E-4KI422-HW encoder is a hardware-based IP core that offers rich features, low latency, and high-quality H.264 (AVC) encoding for UHD Hi422 intra-frame video. It is paired with the AL-H264D-4KI422-HW low-latency decoder, ensuring seamless video processing from capture to display.

Key features of the IP core include:

- Comprehensive modular design with support for user customization and expansion

- Support for intra-frame H.264 and Hi422 5.1 encoding and decoding

- Integrated HDMI 2.0 receiving and transmitting subsystem

- Support for 8/10-bit codec

- Compatibility with RGB, YUV 4:2:2, and 4:4:4 formats

- Low latency of approximately 0.3 seconds

- Support for variable bit rate (VBR) and constant bit rate (CBR)

- Video quality with SSIM above 0.99% or PSNR of 50dB or higher

- Video processing subsystem for pre/post-processing, including color space conversion, scaling, and subsampling

- Support for Gbps Ethernet data stream output

To evaluate our UHD encoding and decoding IP core for 4K @ 60fps performance, we needed a flexible and powerful platform. After careful consideration, we selected the Xilinx ZC706 evaluation kit based on the Zynq Z-7045 SoC for the following reasons:

- A ready-made FMC expansion board provides a 4K HDMI video interface (TB-FMC-HDMI 4K 2.0 daughter card)

- Zynq Z-7045 SoC offers ample programmable logic resources to accommodate the encoder and decoder IP while meeting strict timing requirements

- The SoC integrates a dual-core ARM Cortex-A9 MPCore processor, enabling us to develop custom application software and GUI interfaces

The H.264 encoder supports Hi422 format configuration and 5.1 standard (3840x2160p30) intra-frame encoding. It also supports 10-bit video streaming, preventing any degradation in grayscale or color quality. YUV 4:2:2 support ensures better color accuracy, especially for red tones, which is critical for medical imaging applications.

The block diagram shows the internal structure of the Atria Logic UHD H.264 encoder IP.

Intra-frame coding allows the encoder to achieve minimal frame rate delay. With a macro-module pipeline architecture, the delay is reduced to about 0.3 milliseconds. The pipeline design supports eight pixels per clock, making real-time 4K @ 60fps encoding possible.

The H.264 encoder uses only 78% of the Zynq Z-7045 SoC's programmable logic and DSP resources, and 55% of the available RAM, leaving sufficient space for additional circuits.

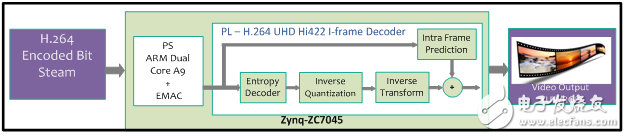

The H.264 decoder supports Hi422 format and 5.1 standard (3840x2160p30) intra-frame decoding. Like the encoder, it supports 10-bit video streams and YUV 4:2:2 format, ensuring accurate color reproduction. It also employs a pipeline architecture to reduce decoding delay.

The block diagram illustrates the internal structure of the Atria Logic UHD H.264 decoder IP.

Low latency is essential for closed-loop human-machine applications. When the AL-H264E-4KI422-HW encoder and AL-H264D-4KI422-HW decoder are connected via an IP network, the total delay is approximately 0.6 milliseconds (excluding transmission time), equivalent to two frames.

The H.264 decoder implementation occupies only 68% of the Zynq Z-7045 SoC’s programmable logic, 35% of the DSP resources, and 45% of the RAM, allowing room for other necessary components.

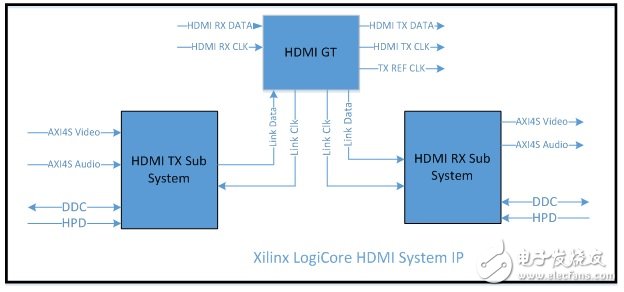

The HDMI subsystem consists of two main modules: the Xilinx LogicCore HDMI TX and RX subsystems. These modules handle the conversion between serial and parallel data, as shown in the following diagram:

The HDMI transceiver (GTX) module handles the conversion between serial HDMI TX/RX data and on-chip parallel data using the Zynq SoC’s high-speed GT transceiver as the HDMI PHY physical layer interface.

The TX subsystem includes a transmission module, AXI Video conversion, video timing control, and an optional HDCP module. It supports 8, 10, and 12-bit data encoding and transmits two to four pixels per clock. The video conversion module converts input AXI-Stream data into a local video format, while the video timing controller generates local video timing. Audio data is sent through the AXI Stream audio interface. The ARM Cortex-A9 processor controls the transmission module via the CPU interface.

The HDMI RX subsystem includes three AXI protocol interfaces. The video conversion bridge captures local video and outputs it as an AXI Stream data stream, conforming to the AXI Design Reference Manual (UG761). The video timing controller measures the video timing, and the received audio is sent out through the AXI Stream audio interface. The CPU interface manages control and status communication with peripheral devices.

The HDCP module is optional and not included in the standard IP core configuration.

Customer Diy Sound Modules, Programmable Sound Chip, Sound Module with Customer Sound

AST Industry Co.,LTD , https://www.astsoundchip.com