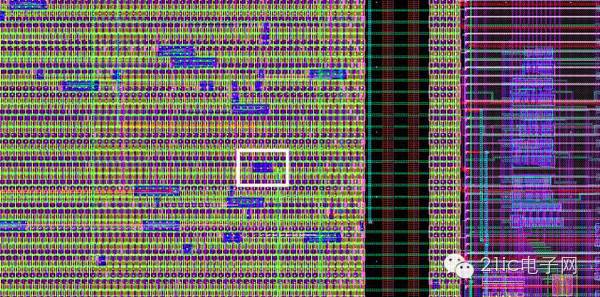

To make a chip, first of all, you have to draw a long-term gadget to Foundry (outsourced wafer fabrication company) (I am worried about copyright issues here... After all, I am also working hard to get other people’s money... Do not put the full circuit diagram... Let's take a look, hope to understand!)

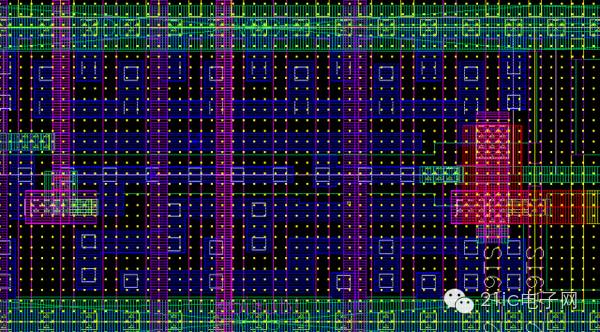

Zoom in again...

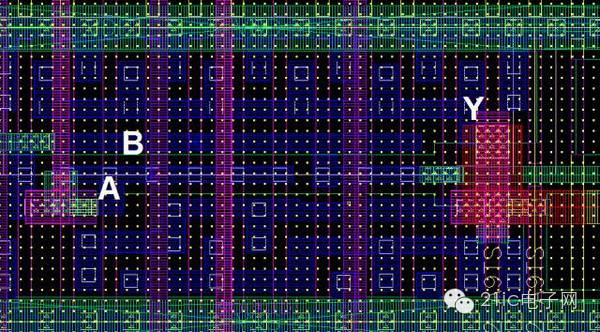

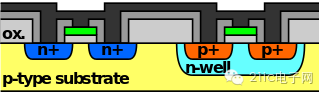

We finally saw a gate! This is a NAND Gate, probably like this:

The pictures are arranged according to the production steps. But the steps are summarized separately.

1. Wet wash (with various reagents to keep the surface of the silicon wafer free of impurities)

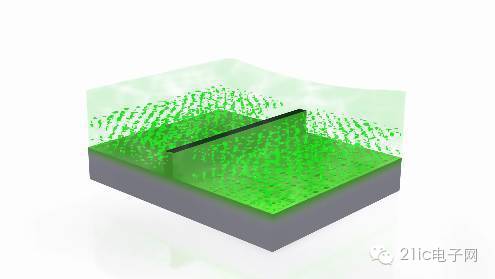

2, lithography (using ultraviolet light to illuminate the silicon wafer through the mask, the place where it is photographed will be easily washed away, and the place where it is not taken will remain as it is. So you can engrave the desired on the silicon wafer The pattern. Note that no impurities have been added at this time, it is still a silicon wafer.)

3. Ion implantation (adding different impurities at different positions on the silicon wafer, different impurities form the FET according to the concentration/position.)

4.1. Dry etching (There are many shapes that have been previously lithographically used, which are not what we need, but are etched for ion implantation. Now we need to wash them off with plasma, or some first-step lithography. Need to engrave the structure, this step is etched).

4.2, wet etching (further wash, but using reagents, so called wet etching).--- After the above steps are completed, the FET has been made ~ but the above steps are generally more than once, it is possible Need to do it over and over again to meet the requirements. ---

5. Plasma rinsing (bombing the entire chip with a weaker plasma beam)

6, heat treatment, which is divided into:

6.1, rapid thermal annealing (that is, the entire film is instantaneously passed through the high-power lamp 到 to 1200 degrees Celsius or more, and then slowly cooled down, in order to enable the injected ions to be better activated and thermally oxidized)

6.2, annealing

6.3, thermal oxidation (manufacturing of silicon dioxide, that is, the gate of the field effect transistor)

7. Chemical vapor deposition (CVD), further fine treatment of various substances on the surface

8, physical vapor deposition (PVD), similar, and can add coating to sensitive parts

9. Molecular Beam Epitaxy (MBE) This is required if long single crystal is required..

10, plating treatment

11, chemical / mechanical surface treatment and then the chip is almost, and then:

12, wafer testing

13, wafer polishing can be factory packaged. Let's take a step by step:

It can be factory packaged. Let's take a step by step look:

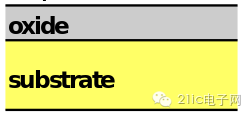

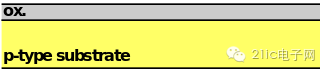

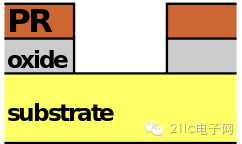

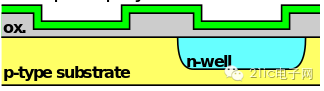

1, the upper is the oxide layer, the bottom is the substrate (silicon) - wet wash

2. Generally speaking, a small amount of (10^10 ~ 10^13 / cm^3) P-type substance (one electron in the outermost layer) is implanted into the entire substrate as a substrate - ion implantation.

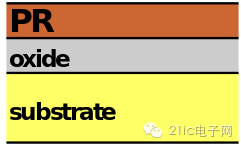

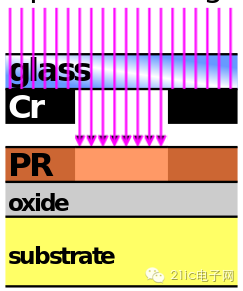

4, the upper mask! (that is where the Cr is marked. The middle empty representation is not covered, the black representation is hidden.) -- Lithography

5, the ultraviolet light goes up... The following is the one that was illuminated - lithography

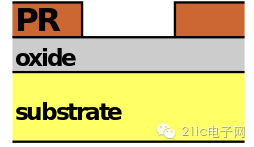

6. Remove the mask. -- Lithography

7. Wash the exposed oxide layer to expose the silicon layer (you can implant ions) -- Lithography

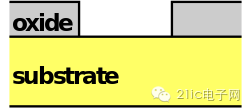

8. Remove the protective layer. This will result in a silicon wafer ready to be implanted. This step will be repeated on the silicon wafer (tens or even hundreds of times).

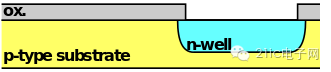

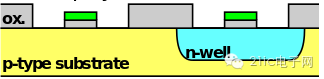

9. After the lithography is completed, insert a small amount (10^14 ~ 10^16 /cm^3) of the injected N-type substance into the inside to make an N-well (N-well)-ion injection

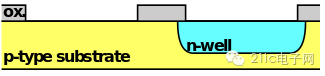

10. Dry etching is used to etch the place where P-well is needed. It can also be etched out again using lithography. -- Dry etching

11. The above figure re-oxidizes a thin layer of silicon dioxide on the upper part of the P-type semiconductor. -- Heat treatment

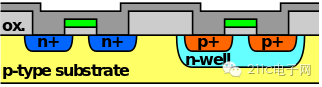

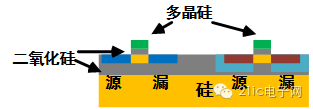

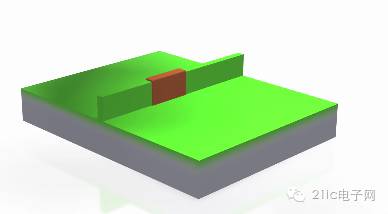

12. Molecular beam epitaxy is used to treat a layer of polycrystalline silicon, which is conductive - molecular beam epitaxy

13. Further etching to make a fine structure. (In annealing and partial CVD) - Repeat 3-8 lithography + wet etching 13 Further etching to make a fine structure. (In annealing and partial CVD) -- Repeat 3-8 lithography + wet etching

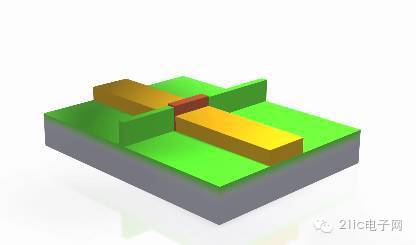

14. Insert a large amount (10^18 ~ 10^20 / cm^3) of injected P/N type material again, and note that the MOSFET has been basically formed. -- Ion implantation

15. Nitride layer formed by vapor phase deposition - chemical vapor deposition

16. Etching nitride out of the channel -- lithography + wet etching

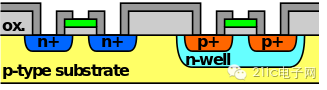

17, the physical vapor deposition of the metal layer - physical vapor deposition

Title: << IC Fabrication Technology >> By BOSE

Let's talk about lithography. The main question is: It is difficult to operate smaller than the diameter of the hair, so how is lithography (say 100nm) done?

For example, if we want to make a 100nm gate (90nm technology), then it is actually like this:

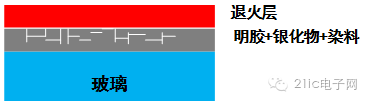

This mask is the first layer, about 10 times the Die Size is made in two ways: Emulsion Mask and Metal MaskEmulsion Mask:

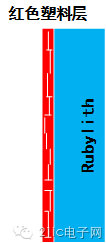

This product resolution can reach 2000line / mm (in fact, very bad ... so sub-micron, that is, VLSI below the um level does not need to ...) This cargo resolution can reach 2000line / mm (in fact, very bad.. So sub-micron, that is, VLSI below the um level does not need to be used...) How to make it: First: You need to engrave a shape 20 times larger than the desired mask on Rubylith (not translated...) (Probably 200 times the actual size of the production), this shape can be carved out with a laser, only a micron scale.

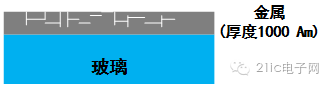

Give it! Photo! Photo! The photo is Emulsion Mask! Give it! Photo! Photo! Emulsion Mask! If the photo to be taken is too large, there is also a method of sub-area. Metal Mask:

Production process:

1. Make an Emulsion Mask first, then use the Emulsion Mask and the 17-18 steps I mentioned before to make the Metal Mask! There is a feeling of Recursion in the moment!

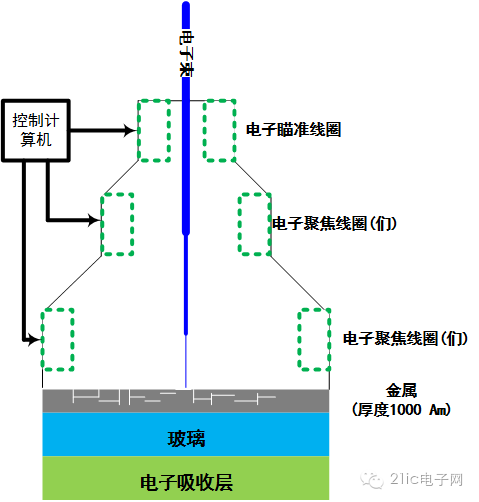

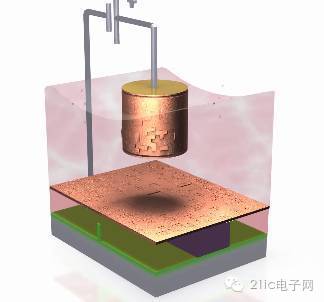

2, Electron beam:

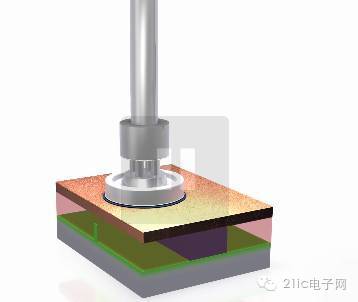

Probably long like this

Just like the printer, just hit it underneath.

The advantage is that the accuracy is particularly high. Most of the high-precision (<100nm technology) uses this mask. The disadvantage is too slow...

After making a mask:

Feature Size = k*lamda / NA

k is generally 0.4, related to the production process; lamda is the wavelength of the light used; NA is the magnification of the magnifying glass as seen from the chip.

At the current state of the art, this formula has changed, because as the Feature Size decreases, the thickness of the lens is also a problem.

Feature Size = k * lamda / NA^2

Well, in fact, the mask can be made larger than the chip. As for the specific production method, it is usually directly carved with a high-precision computer probe + laser. Photomask (mask) material selection is generally more flexible than silicon wafer, can Made from materials that are easily vaporized by laser.

This lithography method is a black technology general point! Directly reduce Lamda by an order of magnitude, With no extra cost! You say no!

Food for Thought: Wikipedia's layout on the mask gives such a picture. What kind of shape would it be made with such a mask?

The steps of the drawing are labeled below each figure for a total of 18 steps.

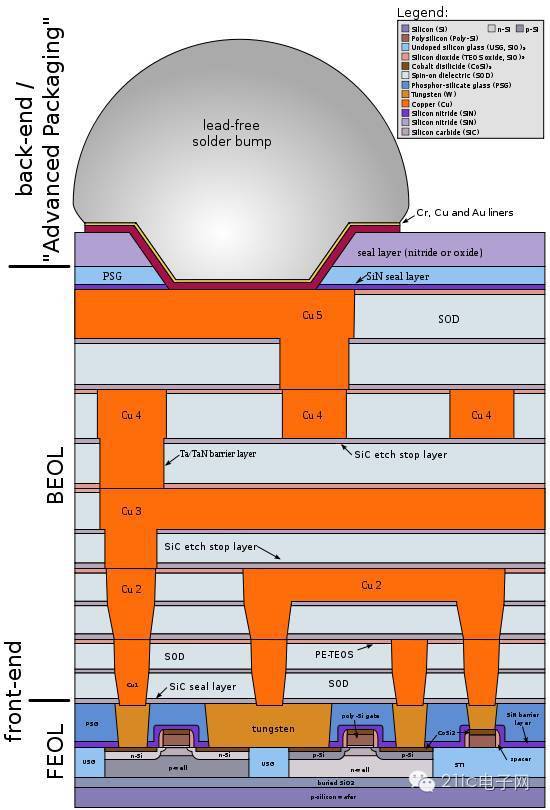

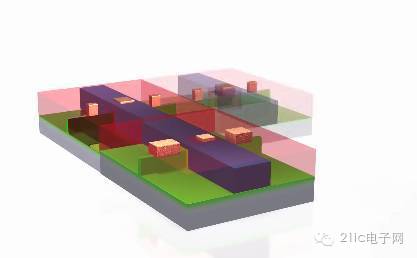

The final shape is probably as long as this:

Among them, steps 1-15 belong to the front-end processing (FEOL), that is, how to make the FET

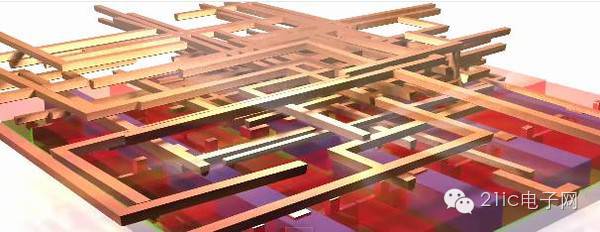

Steps 16-18 (plus a lot of repetitions) belong to the back-end processing (BEOL), the back-end processing is mainly used for wiring. The basics that can be seen in the big chip at the beginning are all wiring! Generally a highly concentrated The underlying silicon chip is almost invisible on the chip and will be blocked by the wiring.

SOI (Silicon-on-Insulator) technology:

The drawbacks of traditional CMOS technology are: The thickness of the substrate affects the parasitic capacitance on the chip, which indirectly leads to the performance degradation of the chip. The SOI technology mainly separates the source/drain and the silicon substrate to achieve (partially) eliminate parasitic capacitance. the goal of.

Tradition:

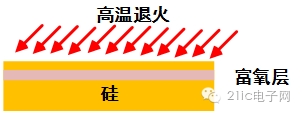

There are mainly the following methods (mainly in the fabrication of silicon-silicon dioxide-silicon structure, the subsequent steps are basically the same as the traditional process.) 1. High temperature oxidation annealing:

Oxygen ions penetrate into the silicon layer to form an oxygen-rich layer

forming.

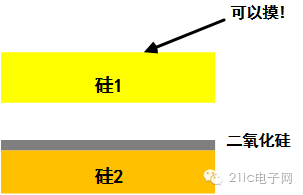

Or 2. Wafer Bonding (with two pieces!) Isn't it the same structure as a sandwich cookie? Yeah is not bad! Come two!

Come two!

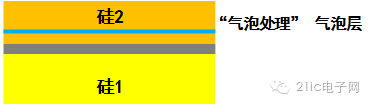

Surface oxidation of silicon 2

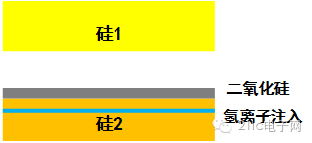

Hydrogen ion implantation of silicon 2 and hydrogen ion implantation of silicon 2

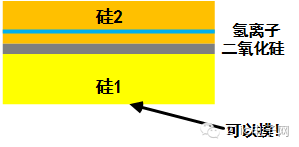

Turn over

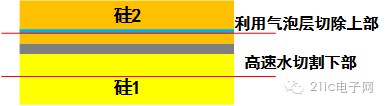

Treating the hydrogen ion layer into a bubble layer and treating the hydrogen ion layer into a bubble layer

Cut off the excess and cut off the excess

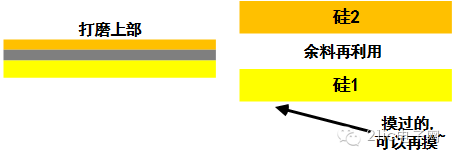

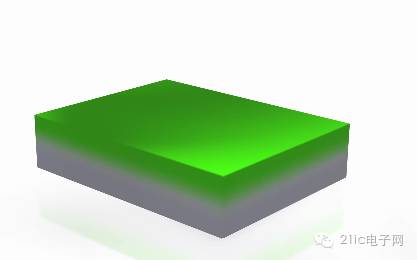

Molding! + Reuse

Lithography

The micrograph is as long as this:

Photolithography + etching

Remove the protection, the middle one is Fin to remove the protection, the middle one is Fin

Polysilicon/high-k dielectric growth of polysilicon/high-k dielectric growth gates at the gate

Oxide layer growth at the gate of the oxide layer in the gate

Growing into this

Source drain fabrication (lithography + ion implantation)

Primary metal/polysilicon patch

Etching + molding

The physical vapor phase grows out of the surface metal layer (because it is a three-dimensional structure, all the wires are connected at the top)

Mechanical grinding (right! Ungrinding will result in inconsistent metal layer thickness)

Molding! Forming!

Probably the sauce purple...

The Smart Screen Protector Cutting Machine can help stores reduce the inventory of Screen Protectors. It is mainly used to cut Screen Protectors such as Mobile Phone Screen Protectors, Watch Screen Protectors, Tablet Screen Protectors, Pad Screen Protectors, and personalized fashion Back Films. It is very suitable for personal business or shop drainage.

Universal Screen Protector Cutting Machine has 20000+ cloud data of different specifications and models, adopts massive cloud database, and all data is updated synchronously in the state of networking. You'll have a full range of screen protector models on one machine and cut any Screen Protector model as needed without having to stock up on Screen Protectors for various phone models. No more losing customers due to missing models.

Screen Protector Cutting Machine,Protective Film Cutting Machine,Back Sticker Cutting Machine,Phone Sticker Cutting Machine, Film Cutting Machine

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.tpuscreenprotector.com